1250

Member

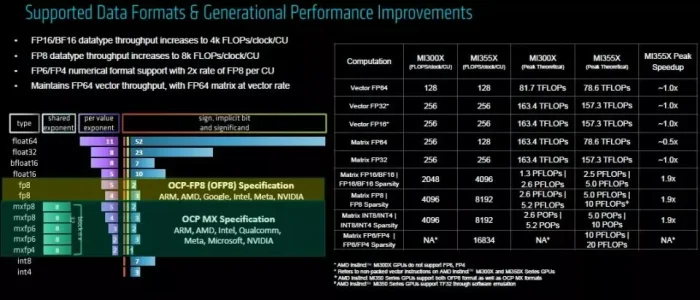

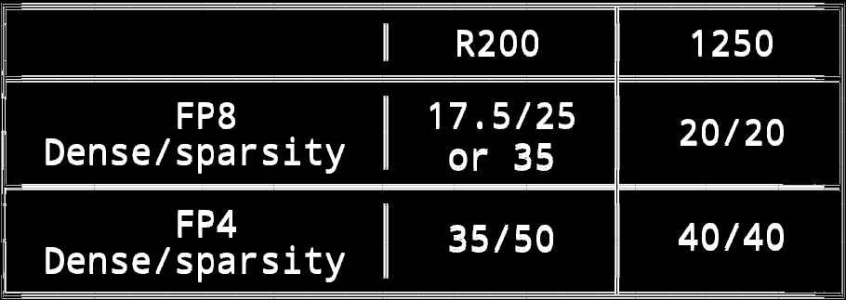

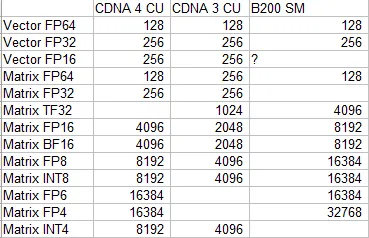

R200=Rubin 1250=MI455X

R200=Rubin 1250=MI455XIn the case of Rubin, it appears that adaptive compression(semianalysis 3:2) has replaced 2:4 structured sparsity.

I am uncertain whether the value is 25 or 35. On the other hand, I've put together a table where the MI455X is listed with the same value.

(https://chipsandcheese.com/p/amds-cdna-4-architecture-announcement)

(https://chipsandcheese.com/p/amds-cdna-4-architecture-announcement)SemiAnalysis stated that FP4 is 32,768, but it seems highly likely that this is a dense value. The matrix value seems to be based on sparsity?

So, to conclude, how accurate would you say top table above is? (25 or 35 etc)

Last edited: