DisEnchantment

Golden Member

Speculate at will

Last edited:

Nice. It is at a parity with 9700X unlike 7800X3D which was slower than 7700X.Highest ST and MT scores posted yet, in one run. 5.269, 2x16 6000

ASUS System Product Name - Geekbench

Benchmark results for an ASUS System Product Name with an AMD Ryzen 7 9800X3D processor.browser.geekbench.com

Thank you for the clarification.It's a Zen Timmings misread. It seems VDDQ and VPP values are exchanged

This *may* all be just guesswork, based on claims from various 3rd parties, not from original information. (Including the part number 100-100001084WOF.)9800X3D listed, 5.2 boost.

Recent GB6 runs also top out at 5.25.

AMD Ryzen 7 9800X3D ab € 428,00 (2026) | Preisvergleich Geizhals Deutschland

✔ Preisvergleich für AMD Ryzen 7 9800X3D ✔ Bewertungen ✔ Produktinfo ⇒ Kerne: 8 (8C) • Threads: 16 • Turbotakt: 5.20GHz • Basistakt: 4.70GHz… ✔ AMD ✔ Testberichte ✔ Günstig kaufengeizhals.de

We should get the RX 9800XT in 2026 unless they decide to reboot the naming scheme. So that combination could exist in a lot of real world PCs.AMD should release a new RX 9800 to go along with 9800X3D. Radeon 9800 Pro was such a legendary GPU back in the ATI days.

Yeah, it's very likely placeholder data that is being corrected as more info comes out.This *may* all be just guesswork, based on claims from various 3rd parties, not from original information. (Including the part number 100-100001084WOF.)

They chose to list the stepping as "GNR-B0" BTW.

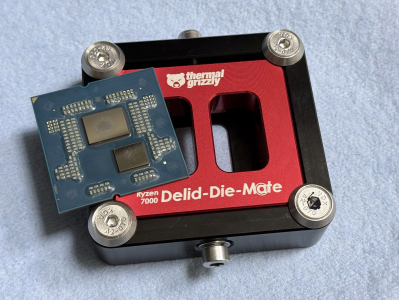

No source provided is kinda sus but don’t have any reason to necessarily doubt this image. Just wish there were more details provided.9800x3d delidded, no V-Cache in sight

View attachment 110431

Here's Your First Look at a Delidded AMD Ryzen 7 9800X3D CPU With Next-Gen 3D V-Cache Tech

AMD's Ryzen 7 9800X3D CPU has been delidded, revealing the next-generation of 3D V-Cache technology innovations for gamers.wccftech.com

Rather odd that they didn’t flag this as an “exclusive”, which they usually do in the past to take credit for being the first source… but I’ll give credit where credit is due and say that they rightfully have the first leak.9800x3d delidded, no V-Cache in sight

View attachment 110431

Here's Your First Look at a Delidded AMD Ryzen 7 9800X3D CPU With Next-Gen 3D V-Cache Tech

AMD's Ryzen 7 9800X3D CPU has been delidded, revealing the next-generation of 3D V-Cache technology innovations for gamers.wccftech.com

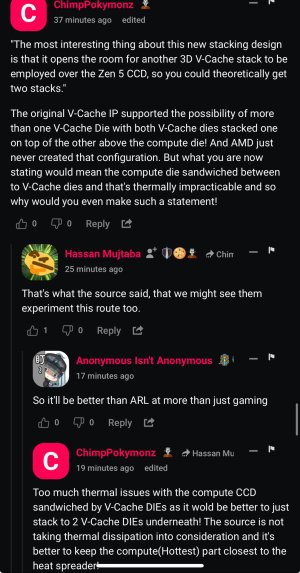

Now why the heck would AMD sandwich the CCD between TWO cache dies?! C’mon! If you want to have multiple cache dies, you either stack them all on top or on the bottom because of how TSVs work. JFC, WTFTech writers are given a sneak peak and they come to the silliest of conclusions. *facepalm*The most interesting thing about this new stacking design is that it opens the room for another 3D V-Cache stack to be employed over the Zen 5 CCD, so you could theoretically get two stacks. This would make for a true stacked chiplet design for the desktop segment. Going such a route will be a bit tricky since power, cost, and thermals have to be kept in mind, but there is definitely a possibility, and maybe we will see such products in the future.

9800x3d delidded, no V-Cache in sight

View attachment 110431

Here's Your First Look at a Delidded AMD Ryzen 7 9800X3D CPU With Next-Gen 3D V-Cache Tech

AMD's Ryzen 7 9800X3D CPU has been delidded, revealing the next-generation of 3D V-Cache technology innovations for gamers.wccftech.com

Rather odd that they didn’t flag this as an “exclusive”, which they usually do in the past to take credit for being the first source… but I’ll give credit where credit is due and say that they rightfully have the first leak.

But then you see idiotic statements like this and you’re reminded of their incompetence.

Now why the heck would AMD sandwich the CCD between TWO cache dies?! C’mon! If you want to have multiple cache dies, you either stack them all on top or on the bottom because of how TSVs work. JFC, WTFTech writers are given a sneak peak and they come to the silliest of conclusions. *facepalm*

Edit: Wow, I found the one sane person in the comments section, and they happen to have the same thoughts as me. Of course, stupid Hassan deflects blame by basically saying “Oh, poor me. Please don’t shoot the messenger, that’s just what my source told me!” I swear to God, these hacks don’t deserve getting exclusive leaks because more than half the time they don’t use critical thinking. It’s like that opening scene in Rush Hour where Chris Tucker’s character, who is a detective, is trying to buy weapons from a guy and gets shown C4 in the back of the guy’s car and he’s all like, “Wow, that’s beautiful, man…. What am I looking at?”

View attachment 110432

9800x3d delidded, no V-Cache in sight

View attachment 110431

Here's Your First Look at a Delidded AMD Ryzen 7 9800X3D CPU With Next-Gen 3D V-Cache Tech

AMD's Ryzen 7 9800X3D CPU has been delidded, revealing the next-generation of 3D V-Cache technology innovations for gamers.wccftech.com

From a quick google this is exactly what other X3D parts look like, both 5800X3D and 7800X3D just look like solid black squares with no apparent structural silicon.9800x3d delidded, no V-Cache in sight

Using the images of Frizchens Fritz:

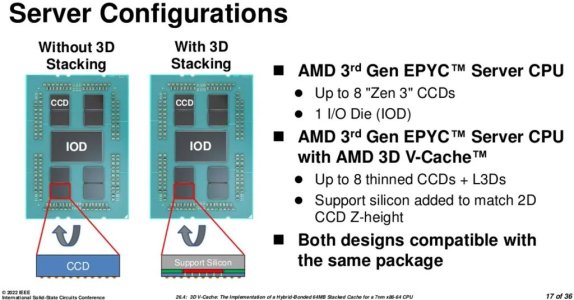

This shows the signal / power interconnects on the AM5 Zen 5 substrate and the ball grid array of the Zen 5 CCD that goes on it.

View attachment 110435

I do not know how you would put the 3D V-Cache die between those two ???

Maybe AMD engineers can do wonders?

The only change which seems possible is that they have flipped the 3D V-cache die so that the TSV's of the CCD now connect directly to the top metal layer of the 3D V-cache.

In this case the 3D V-cache die itself would no longer need TSV's with the result that the total TSV length is halved, reducing the resistance by a factor two.

???? Wat. The iGPU is on the IO die.what is the point of v-cache when big part of die is igpu which is not necessary?

The point of V-cache is

They could use more die area to have more L3 but it adds cost.no

the question is: why can't they fit extra L3 in the die without v-cache?