MLID also clearly said what 20-30% for ARL? So clearly taking his numbers at face value isn't smart.He clearly said 15-25% but you do you.

A couple more points:

This is so hard to believe. LNC had massive, massive core hierarchy changes, and got almost that much IPC gains total.

Doubling the L2 cache can not possibly help that much, and interestingly enough the only cache hierarchy changes that got such a large IPC uplift in specint2017 alone in the "armchair qb GLC" chips and cheese article was switching to Apple's cache hierarchy lol.

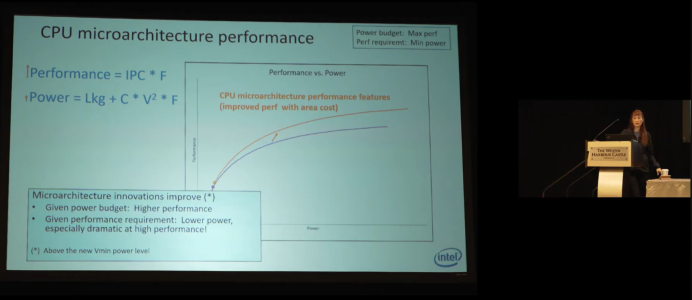

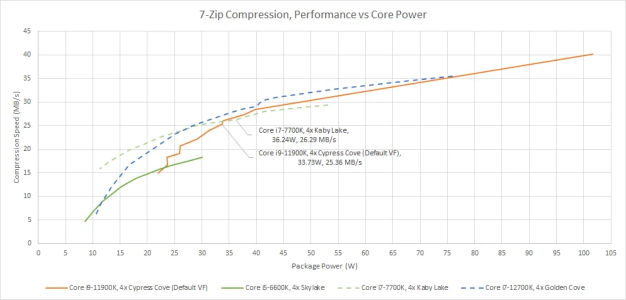

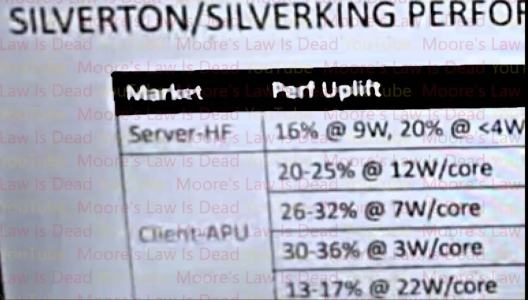

I believe MLID is once again confusing perf uplifts at different power levels with IPC. Just like what he did with RWC, claiming that it would see a 20% IPC uplift because he saw a document claiming RWC would get 20% "power-perf" improvements for server.

Problem is, just like with RWC over RPC, Zen 7 over Zen 6 will have perf improvements attributed to the node uplift as well, at least at mid/low power.

In fact, this document MLID also showed:

Reveals at near Fmax (22 watts per core), the perf uplift is apparently only 13-17%. That is prob the targeted IPC improvement, if Fmax doesn't really improve as well.

Then you have Zen 6 to fix that? If it's just about rightsizing structures and not actually implementing new ideas, that's very plausible even on what should be a "tick" core. Never mind the fact that AMD actually gets good IPC uplifts on "tick" cores as well because of their longer release schedule.And really they're gonna be targeting 20% bare minimum, OG Z5 on N3B was kinda that but they had to roll back and neuter a bunch of core resources.

Also Zen 5 already blew up a lot of core resources compared to how lean previous Zen versions were. I shudder to think what "OG Z5" then would have looked like.

Forgot to add this, but 20% "bare minimum" would make it the largest IPC uplift since OG Zen. Press x to doubt.

How is 2MB plenty? ARM already implements more L2 cache in their P-cores on the exynos 2600 (3MB). And that's the current gen. Zen 7 is 2 years down the line.2MB is plenty, ARM basically tops out there and M5 Super is 1MB.

Plus, there's the issue of AMD slowly increasing CCX core count, esp in server. This will not help the L3 latency situation, which was a huge factor in how performant AMD cores are.

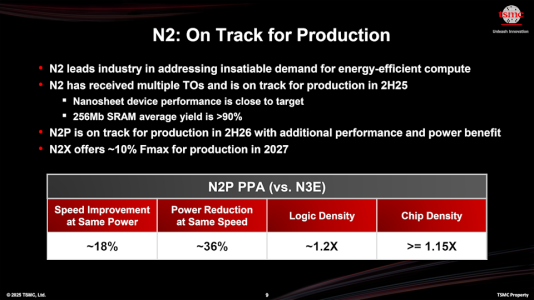

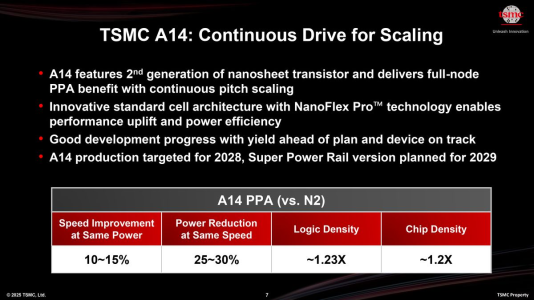

N3 from N5 took 3 years, N3 to N2 took 3 years.Yessir, H2 2028, always 2 years.

A14 taking 2 years from N2 would be them getting back on schedule.