adroc_thurston

Diamond Member

It's not "agree to disagree", it's not an opinion.Agree to disagree.

Xtor count does not define the raw 1t perf.

It's not "agree to disagree", it's not an opinion.Agree to disagree.

Irrespective of the discussion of potential Zen 6 -> 7 gains, that's not necessarily how that works.Core redesigns are bound by transistor count increases..... OR by increased die sizes / decreased profits.

The transistor budget is simply not there for Z7 to improve much ESPECIALLY if they are adding cores to the CCD. I expect the increased L2 is about all they have in them.

DDR8000 will likely also be all the desktop gets with Z7 so no increase over Z6 there.

I applaud your enthusiasm, but it isn't founded on the data present.

Hardly.doing both the process transition and a new uarch is more risky.

I'm ready to simp for ATX12VO too

No, what's expensive is not to scale up their chips yet again, and 3D stacking badly scalable SRAM is probably the only way to do it.By moving it to 3D cache, it does add a good number of process steps (ie more expensive)

It's WoW SoIC.No, what's expensive is not to scale up their chips yet again, and 3D stacking badly scalable SRAM is probably the only way to do it.

H2 25 volume production for what product?

Looking at first products (2H 2026 for N2, rumored 2H 2028 for A14), it would be 2 years.

A14 is Q3'28 products for three vendors.Pretty sure the "2028" date for A14 is based on the same calculations as the "H2 2025" date for N2 was. They did hit that H2 2025 date - TSMC reported it entered mass production in the last few weeks of 2025. It takes months for wafers to make it out the other end of the fab, then there is all that modern packaging, gets shipped to the customer who assembles it into products and those are eventually shipped to customer hands.

It is probably six months for products to come out the other end - longer if you have something you need to have tens of millions already built on launch day like iPhone 18s with A20/A20P SoCs.

I am willing to bet right now that there won't be a single product containing an A14 chip available for sale anytime in 2028. It may be 2028 for "start of mass production" but A14 won't end up in any product you can buy that year. I'm gonna bet when they refine that "2028" down further it'll be H2 or Q4 that it is refined to. Its gonna be three years.

Will they put L2s also on it?It's WoW SoIC.

Very very cheap and simple.

MI400? Venice? Apple?H2 25 volume production for what product?

TSMC has startet HVM for N2 in 2025Looking at first products (2H 2026 for N2, rumored 2H 2028 for A14), it would be 2 years.

...Next, let me talk about our N2 capacity expansion plan. Our practice is to prioritize the land in Taiwan to support the fast ramp of our newest node due to the need for tight integration with R&D operations. Today, our new node, N2, has already entered high-volume manufacturing in the fourth quarter of 2025 with good yield. N2 is ramping successfully in multiple phases at both Hsinchu and Kaohsiung site, supported by strong demand from both smartphone and HPC/AI applications.

Our A14 technology development is on track and progressing well. We are observing a high level of customer interest and engagement from both smartphone and HPC applications. Volume production is scheduled for 2028. Our A14 technology and its derivatives will further extend our technology leadership position and enable TSMC to capture the growth opportunities well into the future.

True.Hardly.

Zen5 is not N3 because N3 was stanky for a hefty while.

Xtor budget in itself is 'free'.True.

But his point is that there's absolutely no way you can do a uarch change without a transistor budget bump, which is just not true.

A14 is Q3'28 products for three vendors.

No?I'll believe it when I see it. To manage that A14 has to enter mass production no later than Q4 2027, so why would TSMC say "2028"?

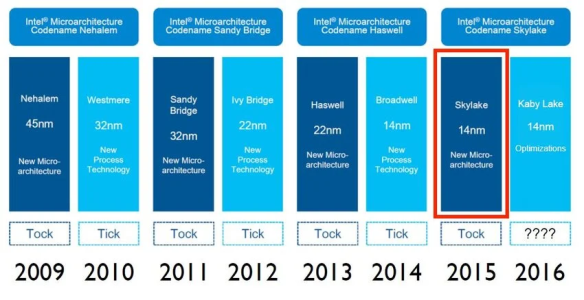

That's what's on the slide used to explain why tock cores improve perf/watt at higher frequencies, not the other way around.Power is the function of uhhhhblh voltage squared, man.

Yes that's what I assumed originally as well....Pretty sure the "2028" date for A14 is based on the same calculations as the "H2 2025" date for N2 was

... but the premise of the leak (zen 7 launching on A14 in 2028) depends on that being the case.I am willing to bet right now that there won't be a single product containing an A14 chip available for sale anytime in 2028.

I think it's BS. Just like how TSMC claimed they hit HVM for N3B in late 2022 and we didn't see a product on it till 3 quarters later...They did hit that H2 2025 date - TSMC reported it entered mass production in the last few weeks of 2025.

.... like what this comment says.In 2022 N3 HVM startet end of year and the first product using N3 was the iPhone Soc. The iPhone went to sale in September 2023.

On the last non delayed node TSMC had (5nm) not counting N2, it took TSMC less than 2 quarters. Same for N7. Both for Apple chips.It takes months for wafers to make it out the other end of the fab, then there is all that modern packaging, gets shipped to the customer who assembles it into products and those are eventually shipped to customer hands.

It is probably six months for products to come out the other end - longer if you have something you need to have tens of millions already built on launch day like iPhone 18s with A20/A20P SoCs.

Unless these products are launching later this half, or at best in June-ish, I don't see how this timeline would apply.MI400? Venice? Apple?

How about L1d cache though?I believe they're moving to separate L1i/OpCache instance per thread to get around the x86 limitations with 4k pages.

Those things exhibit vastly different v/f curves compared to predecessors so none of your observations apply.Every perf/watt curve for every recent tock core: Zen 5, Zen 3, Sunny Cove, exhibited this.

They all exhibit the same thing lolThose things exhibit vastly different v/f curves compared to predecessors so none of your observations apply.

Nah, it's the right voltage, but...Ugh no.

Talk about putting a band aid on a gaping wound! The idea of going single voltage is a good one, but it is way too small a step and 12v is the wrong voltage.

...500W is the wrong power for PC components.We have CPUs that need 500W, GPUs that need even more!

(Let's not go there but 12V would still work fine if Nvidia wasn't an arrogant abusive sod with their special snowflake connector. I'm allergic to people pointing at 48V as if it was ATX voltage that's wrong and not Nvidia's unforced error connector. Nobody had the need for that before this idiocy and the whole world shouldn't have to bend over backwards just so that freshly baked billionaires don't have to admit being wrong.)So you're gonna solve that problem by having a bunch of wires delivering high power with the same stupid architecture but a different motherboard and PSU?

If you're going incompatible you should do it right and go 48v which still falls under 'low power' rules, but then you can use a simple coaxial connector rather than ATX's 24 pins or ATX12VO's 10 pins. With 18 gauge stranded wire that's 500+ watts which handles all mainstream PCs. Higher end builds would use motherboards with multiple connectors (and probably higher gauge wire) to handle those 500W CPUs, 700W GPUs and so forth.

I won't say no to that but you'll probably reinvent something like ATX12VO, anyway. Might as well use the thing that is already here. The only thing that could need improving is probably making sure there's maximum interchangeability with DC power (using external PSU). Going purely DC power is not a good idea exactly for the 500W hardware that you want 48V for - let's not do all that just so that we end up with external ATX PSUs complete with fans.Most PCs would probably dispense with an internal PSU and have a wall wart (though nothing stops you from using an internal PSU if you prefer it) which simplifies cooling and allows for smaller form factors.

While they are it, they could eliminate those fiddly jumper blocks that deserved to die long ago.

ATX12VO is a band aid on terribly outdated design that needs to be tossed out and redone from scratch. If you're going to have incompatible motherboards and PSUs anyway, why not modernize everything rather than take a meaningless step forward that doesn't address any of the real issues?

Yes, different v/f curves.They all exhibit the same thing lol

nope. ATX24VO with industrial cables. Nvidia and Intel keep on pushing watts beyond sanityprobably reinvent something like ATX12VO

i like the picture file name 🙂View attachment 142011

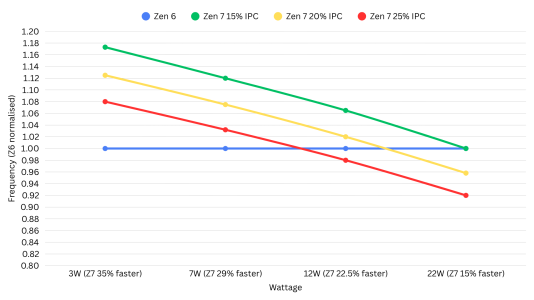

I made a chart to better illustrate the difference IPC has when using the median of the MLID perf/power chart.

As you can see Z7 has a sizeable frequency advantage at low power that diminishes to parity or a deficit at peak power.

Now this is pre-Si so final v/f will only be known in 2028, but it seems like 3-12W is the band of power AMD is optimising for with their classic core.